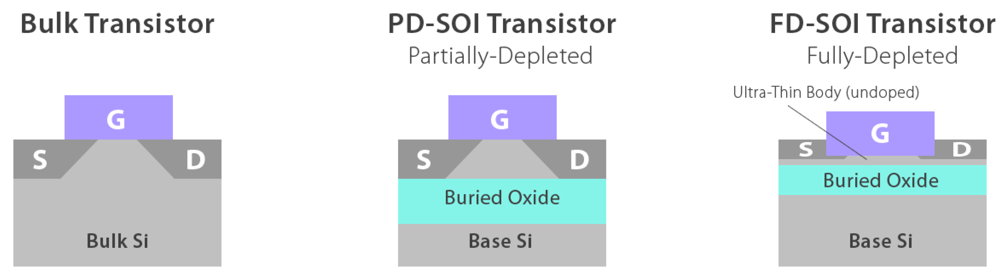

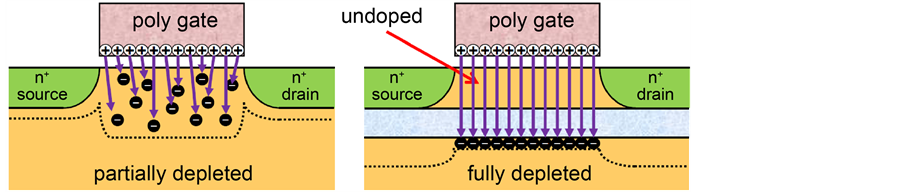

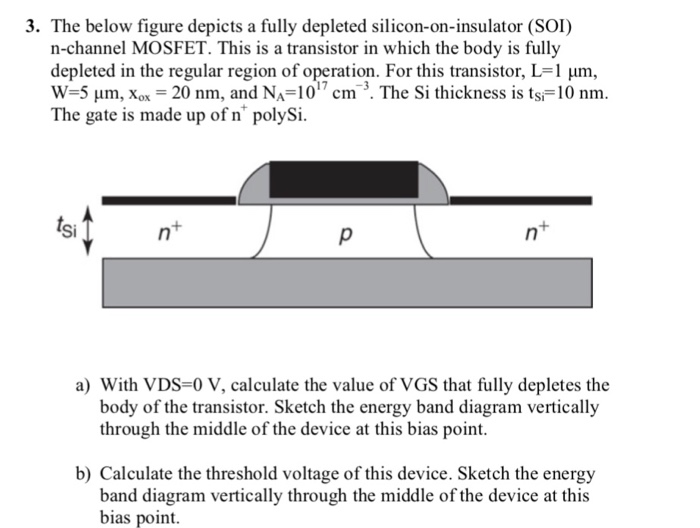

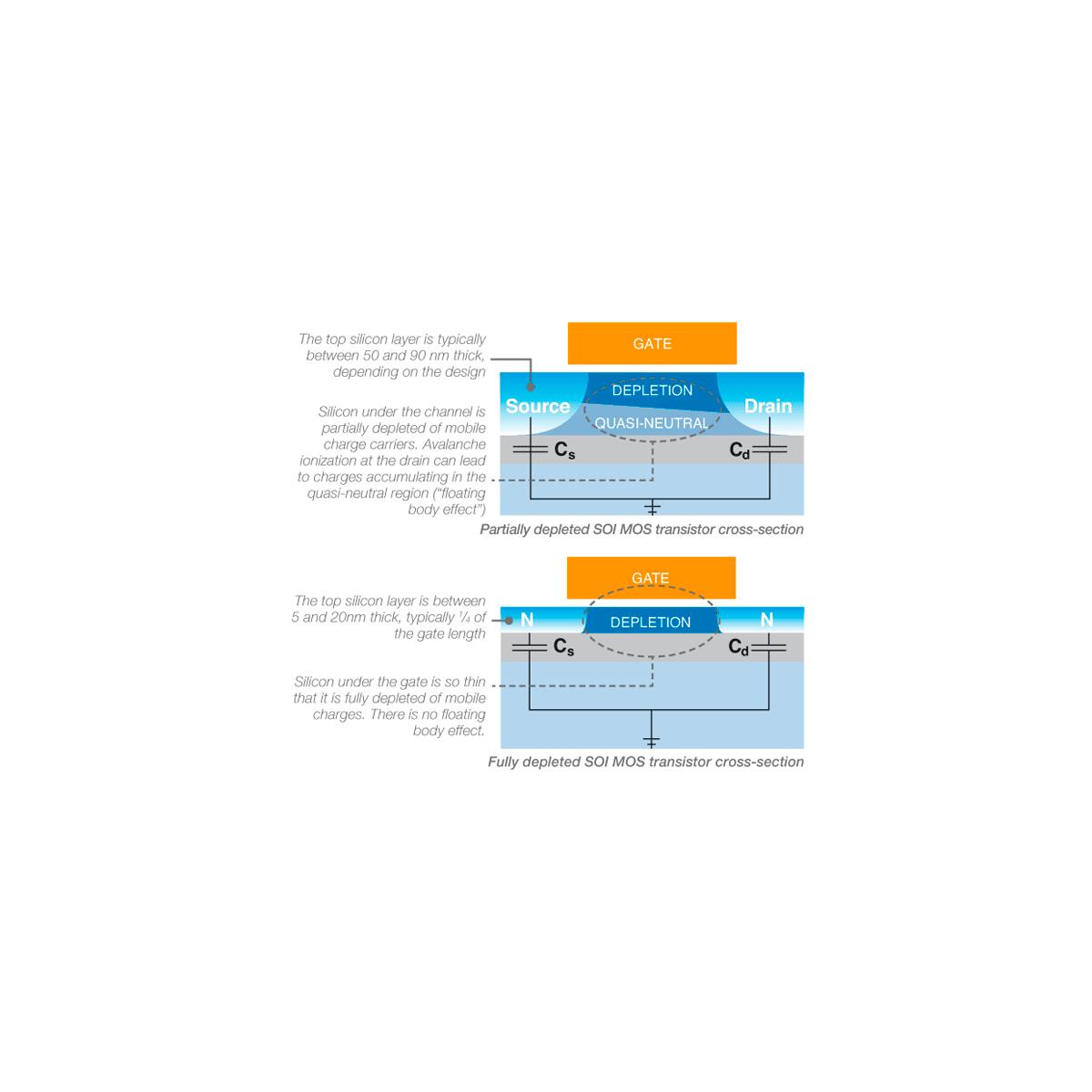

Electrical Characteristics Comparison Between Fully-Depleted SOI MOSFET and Partially-Depleted SOI MOSFET using Silvaco Software

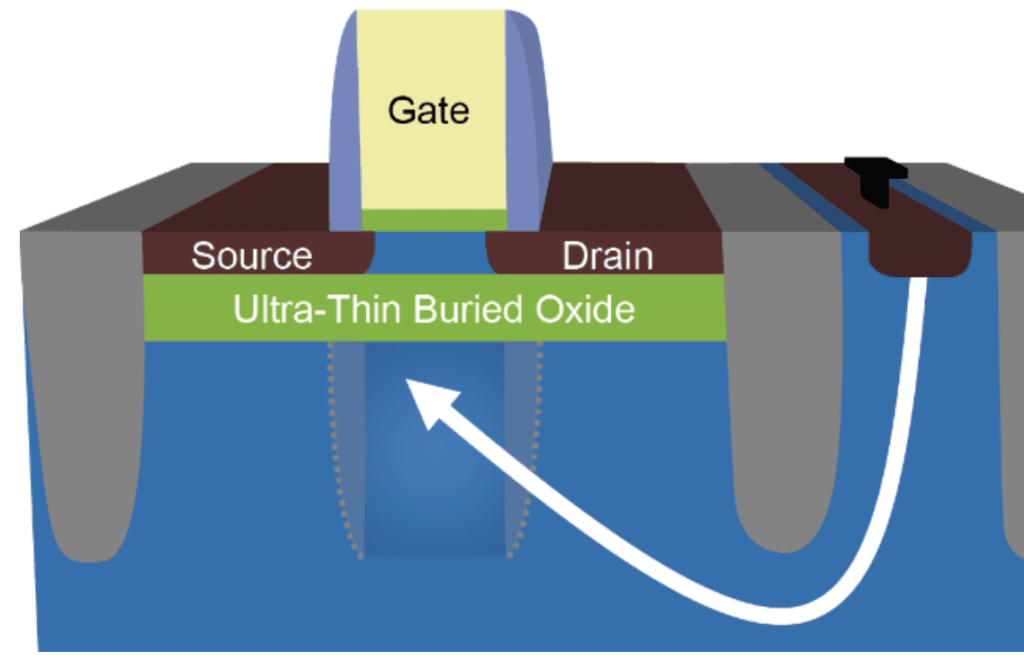

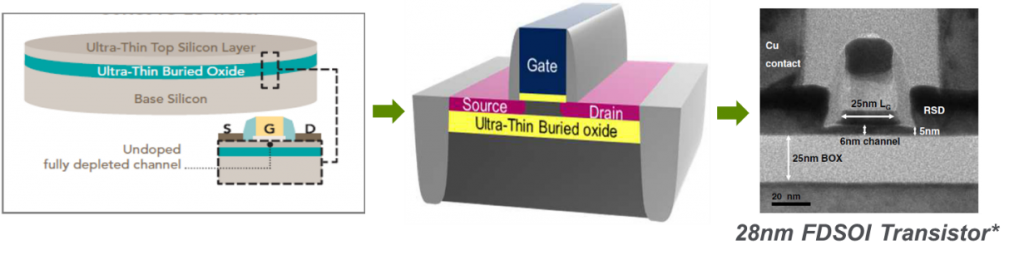

Everything You Need to Know about FDSOI Technology - Advantages, Disadvantages, and Applications of FDSOI - Coventor

Future Outlook: The Advantages of Fully Depleted Silicon on Insulator (FD-SOI) Technology - Coventor

Investigation of veritcal graded channel doping in nanoscale fully-depleted SOI-MOSFET - ScienceDirect

What is the difference between Silicon on Insulator (SOI), Fully Depleted SOI (FDSOI) and Bulk? - Quora

Fully Depleted SOI Characterization by Capacitance Analysis of p-i-n Gated Diodes | Semantic Scholar

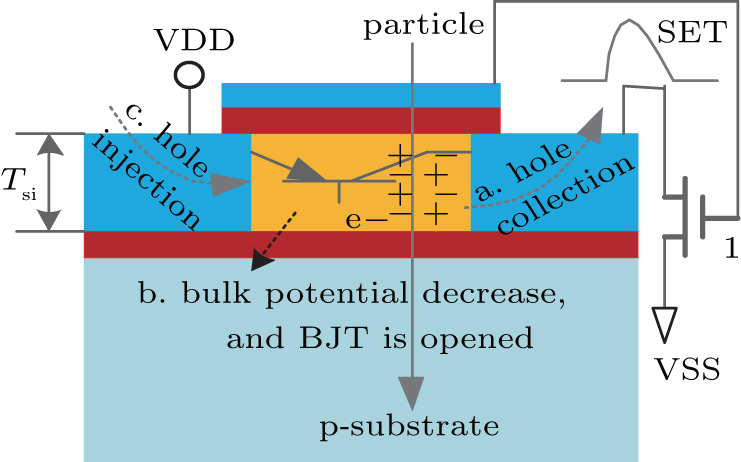

Mechanism of floating body effect mitigation via cutting off source injection in a fully-depleted silicon-on-insulator technology